# Analysis of Power Optimization of Serial Communication Protocol-Memory–Switch Interface

Er. Sukhwinder Kaur<sup>1</sup>, Er Narinder Sharma<sup>2</sup>.

<sup>1</sup>(ECE,Amritsar College of Engg. & Technology/PTU,INDIA) <sup>2</sup>(Assistant Professor, ECE,Amritsar College of Engg. & Technology/PTU, INDIA)

**Abstract:-** Power consumption has rapidly risen to an intolerable scale. This results in both high operating costs and high failure rates so it is now a major cause for concern. It is imposed new challenges to the development of high performance systems. Dynamic power can contribute up to 50% of the total power dissipation. In this paper; we first review the basic power management techniques to reduce the dynamic power consumption techniques like clock gating & frequency scaling. Clock-gating is the most common RTL optimization for reducing dynamic power. We have been also studied I<sup>2</sup>C and SPI are the most commonly used serial protocols for both inter-chip and intra-chip low/medium bandwidth data-transfers. Both protocols are well suited for communications between integrated circuits for slow communication with on-board peripherals.

Keywords:- Register Transfer Level (RTL) Inter- Integrated Circuit (I<sup>2</sup>C), Serial Peripheral Interface (SPI).

## I. INTRODUCTION

Today consumers demands more functionality, speed, energy efficient and power optimized device. A system consists of a set of components that provide a useful behavior or service. Power dissipated on clocklines in a logic chip is approximately 30-50%. Clock signals have been a great source of power dissipation because of high frequency & load. Clock signals do not perform any computation & mainly used for synchronization. Hence these signals are not carrying any information. Gated-clock is one of the most important techniques to reduce power dissipation. By the gated-clock technique, power dissipated on clock lines including synchronous storage elements such as flip-flops and latches can be saved by shutting off the clock of devices when there is no function required. To increase the speed, we have studied two communication protocols SPI & I<sup>2</sup>C. Both SPI and I<sup>2</sup>C offer good support for communication with low-speed devices, but SPI is better suited to applications in which devices transfer data streams, whereas I<sup>2</sup>C is better at multi-master "register access" applications.

## II. LITERATURE REVIEW

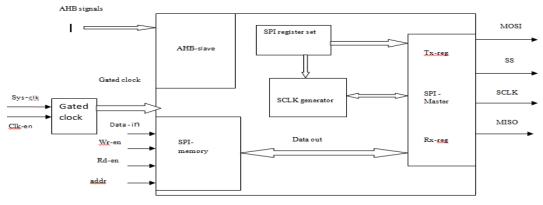

[1] In this paper we studied that the power consumption of AHB SPI-Master is being reduced by using RTL (Register Transfer Level) clock gating technique. Dynamic power can contribute up to 50% of total power. The RTL clock gating technique is used for reducing dynamic power consumption. SPI (Serial Peripheral Interface) is a serial interface which facilitates the synchronous serial data transfer between 2 devices. Dynamic power consumed by the gated clock design is low as compared to non gated clock design.

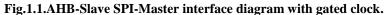

[4] this paper shows that  $I^2C$  (Inter Integrated Circuit) and SPI (Serial Peripheral Interface) are the most commonly used serial protocols for both inter-chip and intra-chip low/medium bandwidth data-transfers. This paper contrasts and compares physical implementation aspects of the two protocols through a number of recent Xilinx's FPGA families, showing up which protocol features are responsible of substantial area overhead. The RTL code is technology independent, inducing around 25% area overhead for  $I^2C$  over SPI, and almost the same delays for both designs. If data must be transferred at "high speed," SPI is clearly the protocol of choice over $I^2C$ . SPI is full-duplex;  $I^2C$  is not. SPI present throughput in the ×100 Mb/s range, but not in Gb/s.[8] this paper describes a design methodology for reducing ASIC power consumption through use of the RTL clock gating feature in Synopsys Power Compiler. This feature causes inactive clocked elements to have clock gating logic automatically inserted which reduces power consumption on those elements to zero when the values stored by those elements are not changing. The methodology was proven in a 200K-gate ASIC, which implemented full scan testing and used RTL clock gating to reduce its power consumption by two-thirds. [9] this paper describes communication protocols the inter-integrated circuit ( $I^2C$ ) and the serial peripheral interface (SPI) protocols. Both protocols are well suited for communications between integrated circuits for slow communication with on-board peripherals.SPI is a single-master communication protocol. SPI has four signals

Fig1.2. A simple SPI communication

- A slave select signal (SSn) for each slave, used to select the slave the master communicates with

- A data line from the master to the slaves, named Master Out-Slave In (MOSI)

- A data line from the slaves to the master, named Master In-Slave Out (MISO).

- A clock signal (SCLK) sent from the bus master **>>** to all slaves; all the SPI signals are synchronous to this clock signal

I<sup>2</sup>C is a multi-master protocol that uses two signal lines. The two I<sup>2</sup>C signals are called serial data (SDA) and serial clock (SCL). There is no need of chip select (slave select). [17] this paper describes Clock gating is one of the power-saving techniques used to save power, clock gating refers to activating the clocks in a logic block only when there is work to be done. Every unit on the chip has a power reduction plan, and almost every Functional Unit Block (FUB) contains clock gating logic. This paper investigates the various clock gating techniques that can be used to optimise power in VLSI circuits at RTL level. [5] This paper describes clock gating is an effective technique for minimizing dynamic power in sequential circuits. Applying clock-gating at gate-level not only saves time compared to implementing clock-gating in the RTL code but also saves power and can easily be automated in the synthesis process. This paper presents simulation results on various types of clock-gating at different hierarchical levels on a serial peripheral interface (SPI) design. In general power savings of about 30% and 36% reduction on toggle rate can be seen with different complex clock-gating methods with respect to no clock-gating in the design.

## III. ANALYSIS USING DIFFERENT TECHNIIQUES AND METHODS

[1] This paper describes the comparison between gated clock design and non- gated clock designs. The following table shows comparison of Dynamic power, LUTs and registers used by both the designs.

| Table1.1. Comparison for 50 MHz clock |                     |                    |             |  |

|---------------------------------------|---------------------|--------------------|-------------|--|

| Sr.<br>No.                            | Features            | Non-Gated<br>Clock | Gated clock |  |

| 1.                                    | Dynamic Power (mW)  | 12.4               | 4.9         |  |

| 2.                                    | Number of LUTS      | 148                | 145         |  |

| 3.                                    | Number of Registers | 35                 | 35          |  |

| Table1.1.   | Comparison | for 5 | 0 MHz     | clock |

|-------------|------------|-------|-----------|-------|

| 1 abic 1.1. | Comparison | 101 5 | O IVIIIIZ | CIUCK |

This paper has proven that overall dynamic power is reduced from 12.4 mW to 4.9 mW by the RTL clock gating.

[4] From this paper we have concluded the practical comparative study of  $I^2C$  and SPI protocols on different FPGA kits. The paper has shown up the results of an up-to-date FPGA implementation of the slave side of the two standard protocols  $I^2C$  /SPI, which are:

- an utilization ratio of 3% and 2% respectively for I<sup>2</sup>C Slave and SPI-Slave on the smallest Viertex-5 FPGA device;

- a maximum transfer rate of 75 MBPS for SPI-Slave;

- and an area overhead of 25% for I2C-Slave over SPI Slave

- •

| Table 1.2 Comparison of occupied slices |                           |                           |             |                                 |             |

|-----------------------------------------|---------------------------|---------------------------|-------------|---------------------------------|-------------|

|                                         |                           | I <sup>2</sup> C- Slave   |             | SPI -Slave                      |             |

| Xilinx's FPGA<br>Device                 | Number of<br>Total Slices | Number of occupied slices | Utilization | Number of<br>occupied<br>slices | Utilization |

| xc2s50-6tq144                           | 768 <sup>*</sup>          | 510                       | 66%         | 363                             | 47%         |

| xc2s50-5tq144                           | 768 <sup>*</sup>          | 503                       | 65%         | 354                             | 46%         |

| xc2v80-6cs144                           | 512 <sup>*</sup>          | 504                       | 98%         | 366                             | 71%         |

| xc4vlx15-12sf363                        | 6114*                     | 512                       | 8%          | 360                             | 5%          |

| xc5vlx30-3ff324                         | $4800^{*}$                | 187                       | 3%          | 141                             | 2%          |

Table 1.2 Comparison of occupied slices

#### Table 1.3 Comparison of delays

|                  | I <sup>2</sup> C- Slave                  |           | SPI -Slave        |           |

|------------------|------------------------------------------|-----------|-------------------|-----------|

| Xilinx'sFPGA     | Xilinx'sFPGA Clock – To- Setup All Paths |           | Clock – To- Setup | All Paths |

| Device           | paths                                    |           | paths             |           |

| xc2s50-6tq144    | 12.079ns                                 | 19.616ns  | 12.234 ns         | 17.042 ns |

| xc2s50-5tq144    | 7.636 ns                                 | 14.996 ns | 7.835 ns          | 12.089 ns |

| xc2v80-6cs144    | 6.483 ns                                 | 12.806ns  | 6.604 ns          | 10.234 ns |

| xc4vlx15-12sf363 | 4.863 ns                                 | 9.572 ns  | 5.006 ns          | 8.880 ns  |

| xc5vlx30-3ff324  | 3.606 ns                                 | 7.998 ns  | 3.303 ns          | 6.971 ns  |

[8] Compares the current consumption of gated clock design and clock design.

| Table 1.4 Current consumption analysis of clock gated design |                        |                           |  |  |

|--------------------------------------------------------------|------------------------|---------------------------|--|--|

| Component                                                    | Current consumption of | Reduced consumption using |  |  |

|                                                              | Non-Gated clock        | Gated clock               |  |  |

| Clock Tree                                                   | 36mA                   | 0%                        |  |  |

| RAMs                                                         | 0mA                    | 100%                      |  |  |

| Flip-flpos                                                   | 32mA                   | 81%                       |  |  |

| Combinational circuitry                                      | 10mA                   | 0%                        |  |  |

| Total                                                        | 78mA                   | 72%                       |  |  |

This paper has proven that by using clock gating dynamic current consumption of a 200K- ASIC reduced from 280mA to 78mA [9] This paper describes the two communication protocol  $I^2C$  and SPI. According to bus topology/routing  $I^2C$  is a winner over SPI. If data must be transferred at "high speed", SPI is

choice over  $I^2C$  because SPI is full -duplex. This paper prove that when there is a need to implement a communication between an integrated circuit such as microcontroller and a set of relatively slows peripherals, there is  $I^2C$  and SPI perfectly fit the bill.

[17] This paper proves that by using RTL clock gating and SPI design power savings of about 30% and 36% with different clock gating techniques in VLSI circuits at RTL level.

### **IV. CONCLUSION**

This paper reviewed techniques and two communication protocols for data transmission for powerefficient system design. Clock gating is the most effective technique to reduce the dynamic power. Both SPI and  $I^2C$  offer good support for communication with low-speed devices, but SPI is better suited to applications in which devices transfer data streams, whereas  $I^2C$  is better at multi-master "register access" applications.

#### REFERENCES

- A. Godara, S. Chaudhary, "Power Consumption Reduction using RTL Clock Gating in AHB Slave-SPI Master Architecture", International Journal of VLSI & Signal Processing Applications, Vol.2, Issue 1 Feb. 2012, pp81-84.

- [2]. Ahuja S. et. al, "System level simulation guided approach to improve the efficacy of clock gating", High Level Design Validation And Test Workshop (HLDVT),2010 IEEE International,10-12 June 2010, Anaheim,pp9-16.

- [3]. A.K. Oudjida et. al, "Design and test of general-purpose SPI Master/Slave IPs on OPB bus", Systems Signals and Devices (SSD), 2010 7th International Multi-Conference ,27-30 June 2010, Amman,pp1-6.

- [4]. A.K. Oudjida et. al, "FPGA implementation of SPI andI<sup>2</sup>C protocols" ISBN No. 978-1-4244-5091-6/09/ 2009IEEE.

- [5]. Bhutada, R. Manoli, Y.,"Complex clock gating with integrated clock gating logic cell", Design & Technology of Integrated Systems in Nanoscale Era, 2007. DTIS. International Conference, 2-5 Sept. 2007,Rabat,pp164 – 169.

- [6]. C. Sharma, A. Godara, "AHB Interface with SPI by using VERILOG", International Journal of Advances in Engineering Research (IJAER), Vol. No. 2, Issue No. VI, Dec.2011.

- [7]. Darold Wobschall, HariSai Prasad, "Esbus -A Sensor Bus based on the SPI Serial Interface",0-7803-7454-1/02© 2002.

- [8]. Frank Emnett and Mark Biegel, "Power Reduction through RTL clock gating", Automotive Integrated Electronics Corporation, 2000.

- [9]. Frederic Leens, "An Introduction to I2C and SPI Protocols", IEEE Instrumentation & Measurement Magazine, 1094-6968/09©2009IEEE.

- [10]. Macii, E., "RTL power estimation and optimization", Integrated Circuits and Systems Design, 2004. SBCCI 2004. 17th Symposium ,7-11 Sept. 2004, Politecnico di Torino, Italy.

- [11]. Manish Kumar Sexana , Ekanash Bhatnaga," Reconfigurable Architecture for IP Peripherals", The International Conference On Signals And Electronic System, September 7-10,2010,Poland,pp347-350.

- [12]. M.K Mdarsha et. al, " Characteristics of Serial Peripheral Interface (SPI) Timing Parameters for Optical Mouse Sensor", Year 2006 IEEE.

- [13]. Matthew Turner and John Naber," The Design of a Bi-directional, RFID- based ASIC for Interfacing with SPI BUS Peripherals", IEEE 978-1-4244-7773-9/10©2010 pp554-557.

- [14]. Papachristou ,Christos A., "A multiple clocking scheme for low-power RTL design", Very Large Scale Integration (VLSI) Systems, IEEE Transactions, Volume no.7, June 1999, pp266 – 276.

- [15]. Paul Myers," Interfacing using serial protocols: SPI and I<sup>2</sup>C", EMRT Consultants, 2005.

- [16]. Qi Wang, Roy. S, "RTL power optimization with gate –level accuracy", Computer Aided Design,2003.ICCAD-2003,International Conference,9-13 Nov,2003,1-58113-762-1,pp39-45.

- [17]. Shinde J,S. Alankar, S.S., "Clock gating A power optimizing technique for VLSI circuits", India Conference (INDICON), 2011 Annual IEEE 16-18, Hyderabad Dec. 2011, pp1 – 4.

- [18]. Suliaman, D.R., "Using clock gating technique for energy reduction in portable computer", Computer & Communication Engineering, ICCCE May2008,Kuala Lumpur, International Conference ,13-15,pp839-842.

- [19]. Takeshi Kitahara et. al, "A Clock –Gating Method for Low Power LSI Design", Semiconductor DA & Test Engineering Centre Toshiba Corporation.

- [20]. Thalluri, L. et. al, "Design of low power and high performance router using dynamic power reduction technique", Devices Circuits and Systems (ICDCS), 2012 International Conference, 15-16 March 2012, Coimbatore ,pp49 – 53.

- [21]. Vyagrheswarudu, N.; Das, S.; .Ranjan.A"Power Adviser: An RTL power platform for interactive sequential optimizations", Design, Automation & Test in Europe Conference & Exhibition (DATE),

2012: 12-16 Takeshi Kitahara et. al, "A Clock –Gating Method for Low – Power LSI Design", Semiconductor DA & Test Engineering Centre Toshiba Corporation.

- [22]. www.soccentrAl.com/results.asp?CatID=488&EntryID=28753

- [23]. Xin Man,Kimura, S." Comparison of optimized multi-stage clock gating with structural gating approach" TENCON 2011 2011 IEEE Region 10 Conference, 21-24 Nov. 2011, pp651 656.